Скачать с ютуб ES3-3- "ADC-based Wireline Transceivers" - Yohan Frans в хорошем качестве

Из-за периодической блокировки нашего сайта РКН сервисами, просим воспользоваться резервным адресом:

Загрузить через ClipSave.ruСкачать бесплатно ES3-3- "ADC-based Wireline Transceivers" - Yohan Frans в качестве 4к (2к / 1080p)

У нас вы можете посмотреть бесплатно ES3-3- "ADC-based Wireline Transceivers" - Yohan Frans или скачать в максимальном доступном качестве, которое было загружено на ютуб. Для скачивания выберите вариант из формы ниже:

Загрузить музыку / рингтон ES3-3- "ADC-based Wireline Transceivers" - Yohan Frans в формате MP3:

Если кнопки скачивания не

загрузились

НАЖМИТЕ ЗДЕСЬ или обновите страницу

Если возникают проблемы со скачиванием, пожалуйста напишите в поддержку по адресу внизу

страницы.

Спасибо за использование сервиса savevideohd.ru

ES3-3- "ADC-based Wireline Transceivers" - Yohan Frans

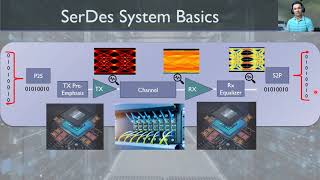

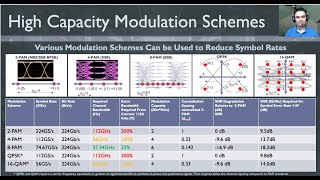

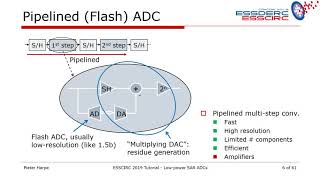

Abstract: The emergence of PAM4 electrical signaling standard at 56Gb/s and 112Gb/s has caused wider adoption of ADC-based transceiver. In this talk, we will start with a high level overview of ADC-based transceiver and its power/performance comparison to the analog/mixed-signal transceiver. We will then discuss more detailed aspects of ADC-based transceiver design such as adaptive hybrid equalization in analog and digital domain, RX Front-end design, ADC requirement and design considerations, and clocking architecture. Biography: Yohan Frans received B.S. degree in electrical engineering from Bandung Institute of Technology, Indonesia in 1995 and M.S. degree in electrical engineering from Stanford University, California in 2001. From 2001 to 2012, he was with Rambus Inc. where he worked on high-performance and low-power serial links and memory interfaces as circuit design engineer, circuit architect, and design manager. Since 2012 he has been with Xilinx Inc, San Jose, CA. He is currently leading design teams as Senior Engineering Director in Xilinx Serdes Technology Group, developing high-speed wireline transceivers for advanced FPGA. His current interests include high-speed mixed-signal circuit design, serial link architecture, transmitter/receiver design, PLL/DLL, memory interfaces, and low-power circuit architectures. He is a member of ISSCC Wireline Sub-committee. For 50% off SSCS membership use code 50SSCS22MEMAMG - https://bit.ly/3ocPzMv