Скачать с ютуб Introduction to FPGA Part 10 - Metastability and Clock Domain Crossing | Digi-Key Electronics в хорошем качестве

Из-за периодической блокировки нашего сайта РКН сервисами, просим воспользоваться резервным адресом:

Загрузить через ClipSave.ruСкачать бесплатно Introduction to FPGA Part 10 - Metastability and Clock Domain Crossing | Digi-Key Electronics в качестве 4к (2к / 1080p)

У нас вы можете посмотреть бесплатно Introduction to FPGA Part 10 - Metastability and Clock Domain Crossing | Digi-Key Electronics или скачать в максимальном доступном качестве, которое было загружено на ютуб. Для скачивания выберите вариант из формы ниже:

Загрузить музыку / рингтон Introduction to FPGA Part 10 - Metastability and Clock Domain Crossing | Digi-Key Electronics в формате MP3:

Если кнопки скачивания не

загрузились

НАЖМИТЕ ЗДЕСЬ или обновите страницу

Если возникают проблемы со скачиванием, пожалуйста напишите в поддержку по адресу внизу

страницы.

Спасибо за использование сервиса savevideohd.ru

Introduction to FPGA Part 10 - Metastability and Clock Domain Crossing | Digi-Key Electronics

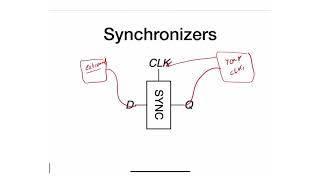

A field-programmable gate array (FPGA) is an integrated circuit (IC) that lets you implement custom digital circuits. You can use an FPGA to create optimized digital logic for things like digital signal processing (DSP), machine learning, and cryptocurrency mining. Because of the FPGA’s flexibility, you can often implement entire processors using its digital logic. You can find FPGAs in consumer electronics, satellites, and in servers used to perform specialized calculations. In this series, we will see how an FPGA works and demonstrate how to create custom digital logic using the Verilog hardware description language (HDL). Previously, we showed how to use a phase-locked loop (PLL) to increase clock speed as well as introduced the concept of glitches. In this episode, we examine how setup and hold time violations can cause metastability in flip-flops. The solution to the challenge at the end of the episode can be found here: https://www.digikey.com/en/maker/proj... All code examples and solutions for this series can be found here: https://github.com/ShawnHymel/introdu... Colin O’Flynn’s metastability experiment: https://colinoflynn.com/2020/12/exper... Better clock divider example: https://github.com/ShawnHymel/introdu... Better button debounce design: https://github.com/ShawnHymel/introdu... Clifford Cummings’s FIFO paper: http://www.sunburst-design.com/papers... A flip-flop requires the input signal to be steady for some time before the clock edge (setup time) and remain steady for some time after the clock edge (hold time). If the input signal transitions during the setup or hold windows, then it is considered a timing violation. This could potentially cause metastability on the flip-flop, where the output remains in an unknown state for some indeterminate amount of time. Normally, the metastable output will settle on logic high or logic low quickly (within a few nanoseconds), but it is not guaranteed. Metastable events can cause potentially catastrophic failures in a design and can be very difficult to track down due to their probabilistic nature. The standard fix to mitigate the likelihood and impact of metastability is to use a synchronizer circuit, which consists of 2 or more flip-flops chained together. The input of one flip-flop samples the output of another. Note that this introduces an extra clock cycle of delay for each flip-flop you put in the chain. A first-in, first-out (FIFO) system is one way to pass data from one class domain to another. Elements are read from the FIFO in the order in which they were written. We can use dual-port block RAM to construct a FIFO in our iCE40. Your challenge is to implement Clifford Cummings’s FIFO design and test it via simulation. Product Links: https://www.digikey.com/en/products/d... Related Videos: • Cyclone® III FPGA • Power Management: Powering FPGAs • FPGA's: Low-Cost, High Performance Sp... Related Project Links: https://www.digikey.com/en/maker/proj... Related Articles: https://www.digikey.com/en/pdf/r/rene... https://www.digikey.com/en/videos/d/d... Learn more: Maker.io - https://www.digikey.com/en/maker Digi-Key’s Blog – TheCircuit https://www.digikey.com/en/blog Connect with Digi-Key on Facebook / digikey.electronics And follow us on Twitter / digikey